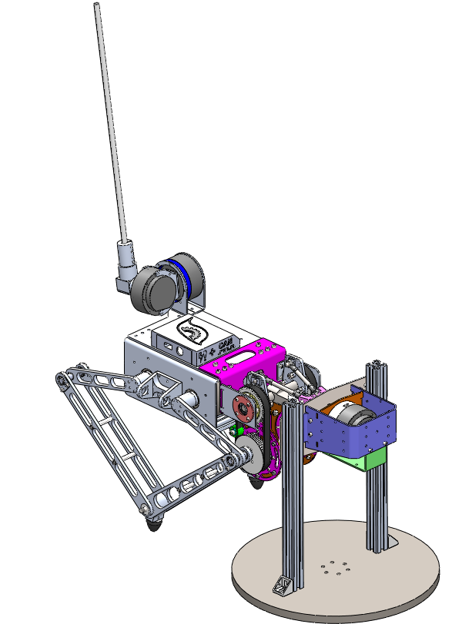

3-DOF Cheetah Inspired Spine

2025

A 3-DOF cheetah inspired spine designed and manufactured for a 9-DOF legged robotic platform to investigate the role of the tail in agile locomotion at the African Robotics Unit, University of Cape Town.

This project involved prototyping various spine solutions, CAD design, full mechanical desing analysis and then manufacturing of the spine. Unfortunately, the full robot was not fully validated before my internship finshed but the simulation video below shows the a proof of concept. In this video the roll axis of the spine is actauted using a triangular torque ramp signal. This is supposed to simulate the disturbance injected to the hindlegs of the cheetah during agile manoeuvres. The tail (unctrolled in this case), acting as counter-weight, significantly reduces the roll of the hind-quarters.

This video shows the initial validation of the 3-DOF spine with only the yaw and pitch differential motor connected and being controlled using an impedance controller.

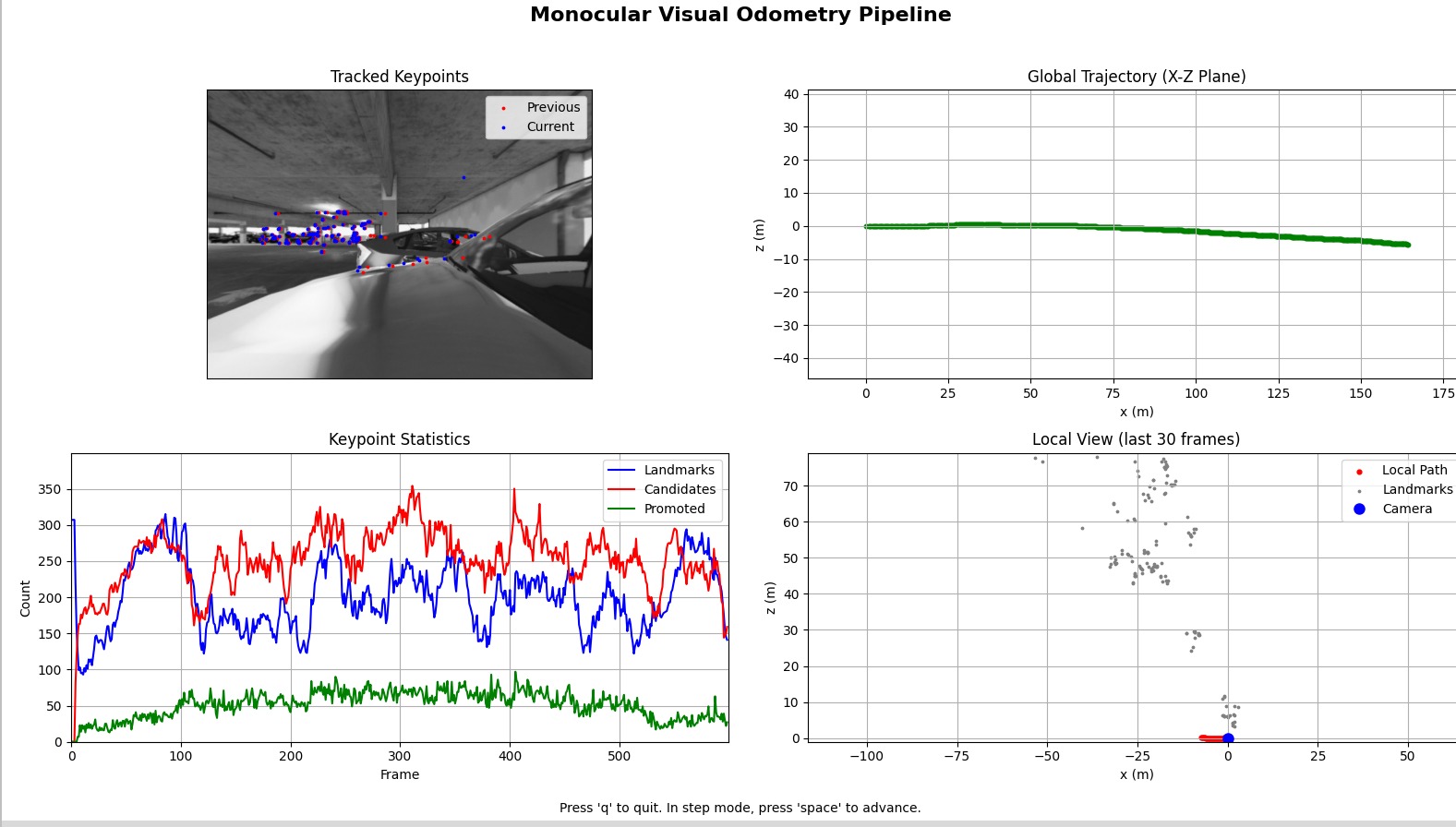

Tokyo Drift: Monocular VO/VIO

2025

Monocular Visual Odometry (VO/VIO) pipeline for 6-DoF trajectory estimation using popular autonomous driving datasets (KITTI, Malaga) in Python. Check out the videos here.

Implemented a bootstrapping approach that initialises a 3D point cloud from two keyframes and continuously uses 2D–3D correspondences to estimate camera motion. The system is being extended to a tightly coupled Visual–Inertial Odometry (VIO) pipeline using a Multi-State Constraint Kalman Filter (MSCKF) to fuse IMU data and mitigate scale drift inherent to monocular setups.

GitHubDexterous Manipulation Learning (RL & IL)

2025

Massively parallelised Reinforcement Learning (RL) and Diffusion-based Imitation Learning (IL) for dexterous manipulation tasks using the ORCA robotic hand.

Part of the Real World Robotics course at ETH Zurich. The course comprised two major projects. The first focused on in-hand cube rotation using RL trained in simulation and deployed via Sim2Real techniques. Policies achieved 6.0 rotations/min using domain randomisation, reward tuning, and regularisation. For the, second, imitation learning project, an architecture search showed that DINOv3 backbones combined with Diffusion Policy outperform alternatives (DINOv2 and ResNet as visual backbones, and ACT as policy) for multi-colour object sorting.

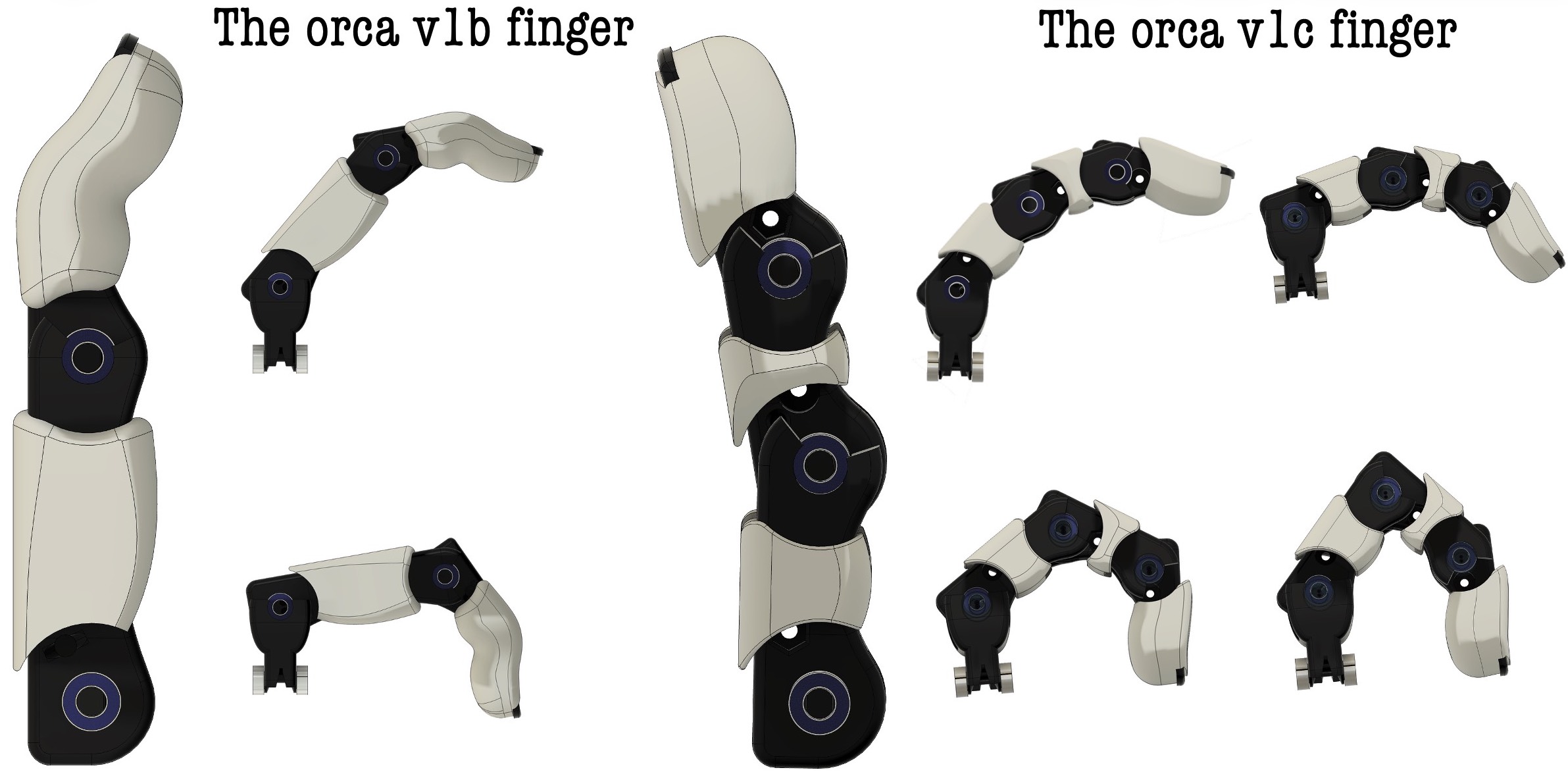

ORCA Hand: PIP–DIP Coupling

2025

Designed a mechanical modification to the open-source ORCA hand that introduces a coupled Distal Interphalangeal (DIP) joint. The image above compares the original ORCA hand (left) with the modified PIP–DIP coupled joint (right).

Inspired by human biomechanical synergies, this project introduces distal articulation coupled to the PIP joint to reduce control complexity while improving dexterity. Criss-cross tendon routing with a target PIP–DIP ratio of 0.7 was used to expand the fingertip workspace and improve grasp robustness on small-diameter objects compared to the original design.

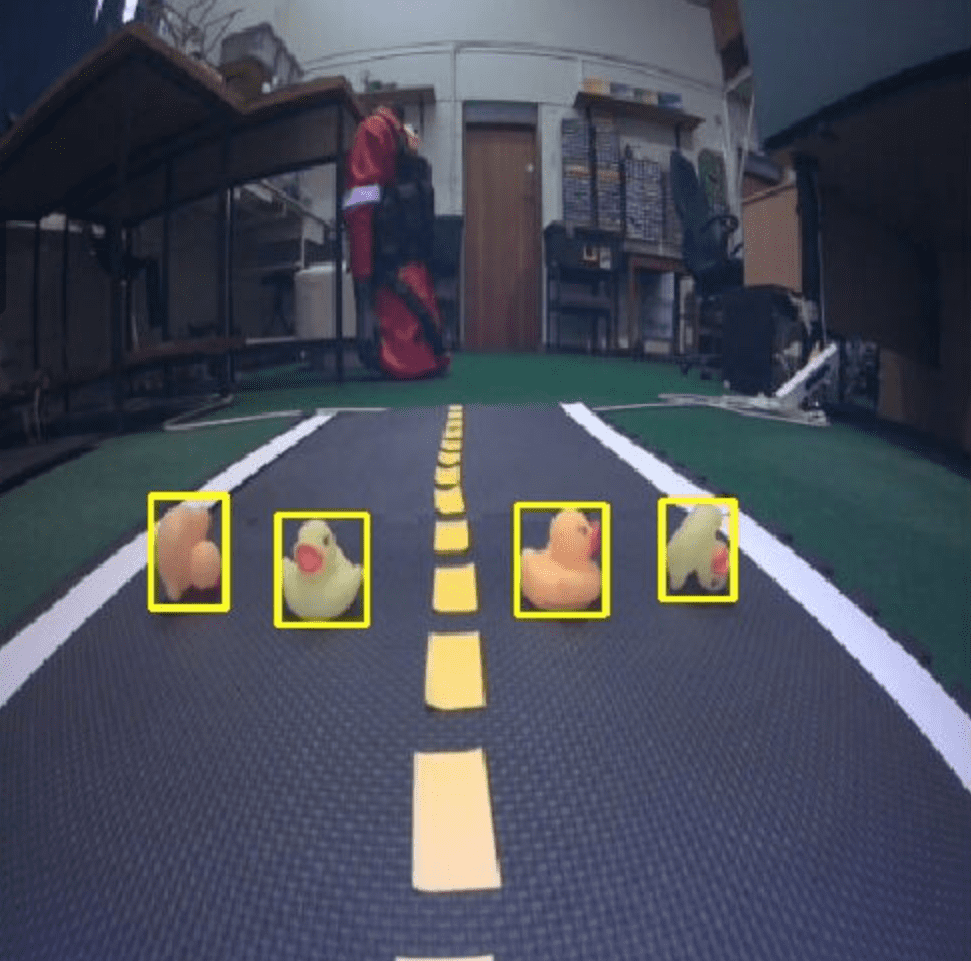

Object Detection for the Duckiebot

2023

Obstacle avoidance implemented using Yolov5 for object detection and a reactive Braitenberg controller on the Duckiebot platform. This project ranked within the top 10 among 2023 final-year projects.

Final-year undergraduate project to investigate the Duckiebot platform for Machine Learning by implementing an object detection model. A pre-trained YOLOv5 model, fine-tuned with a publicly available Duckietown dataset, was utilised to detect Duckietown-specific objects in Python.

To enable autonomous object avoidance, a simple Braitenberg controller was employed. The final solution could detect objects (duckies) in the scene and compute wheel commands to avoid the objects for relatively simple scenarios. The project formed a foundational model that future students can improve and build upon for more sophisticated behaviors.

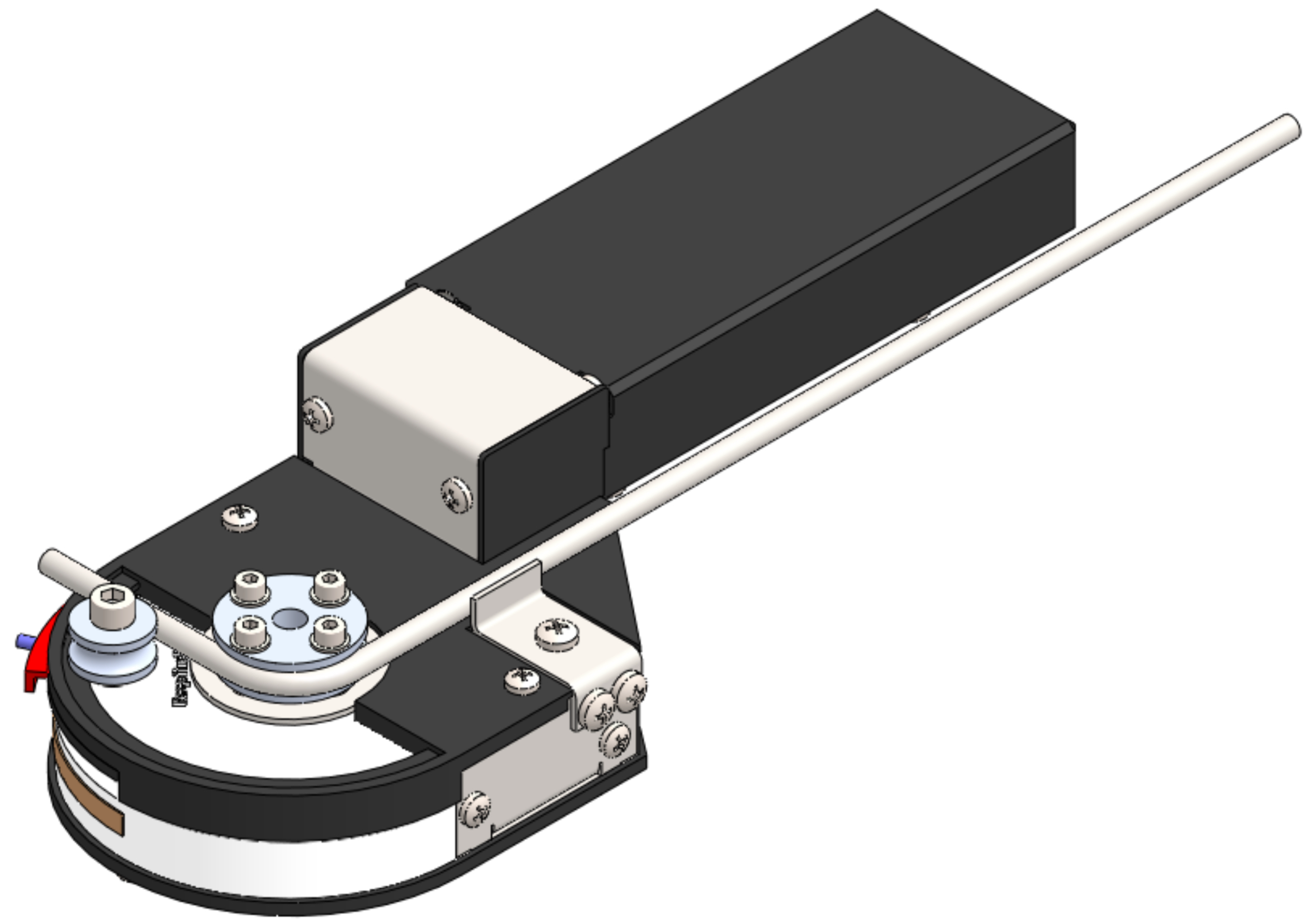

Hand-Held, 6.4V Pipe Bender

2023

A device designed to bend 6mm steel pipes with an inner diameter of 3mm for bend angles up to 90 degrees.

The year-long process was designed to follow the general Product Development Process of concept generation, basic design, detail design, design for prototyping, parts procurement, and testing. Design decisions had to be motivated by rigorous calculations based on mechanical strength, output torque, amperage, etc. that optimized or accounted for the various URs. Where calculations were unfeasible, sound engineering judgment had to be employed with a valid explanation. A 3D CAD model was generated using the various outputs of detail design.

Finally, all the design parts were obtained from the workshop, and the model was integrated. This was an empowering moment when the product was finally in hand after being designed entirely from a sketch. In the final demonstration, the product achieved all the URs except for being able to bend the strongest 6mm Carbon Steel pipe. It was diagnosed that the plastic covers around the bending arm were generating friction when loaded, which was unaccounted for. Despite this, I was extremely proud of the product my team put together and was seeded with a passion for design.

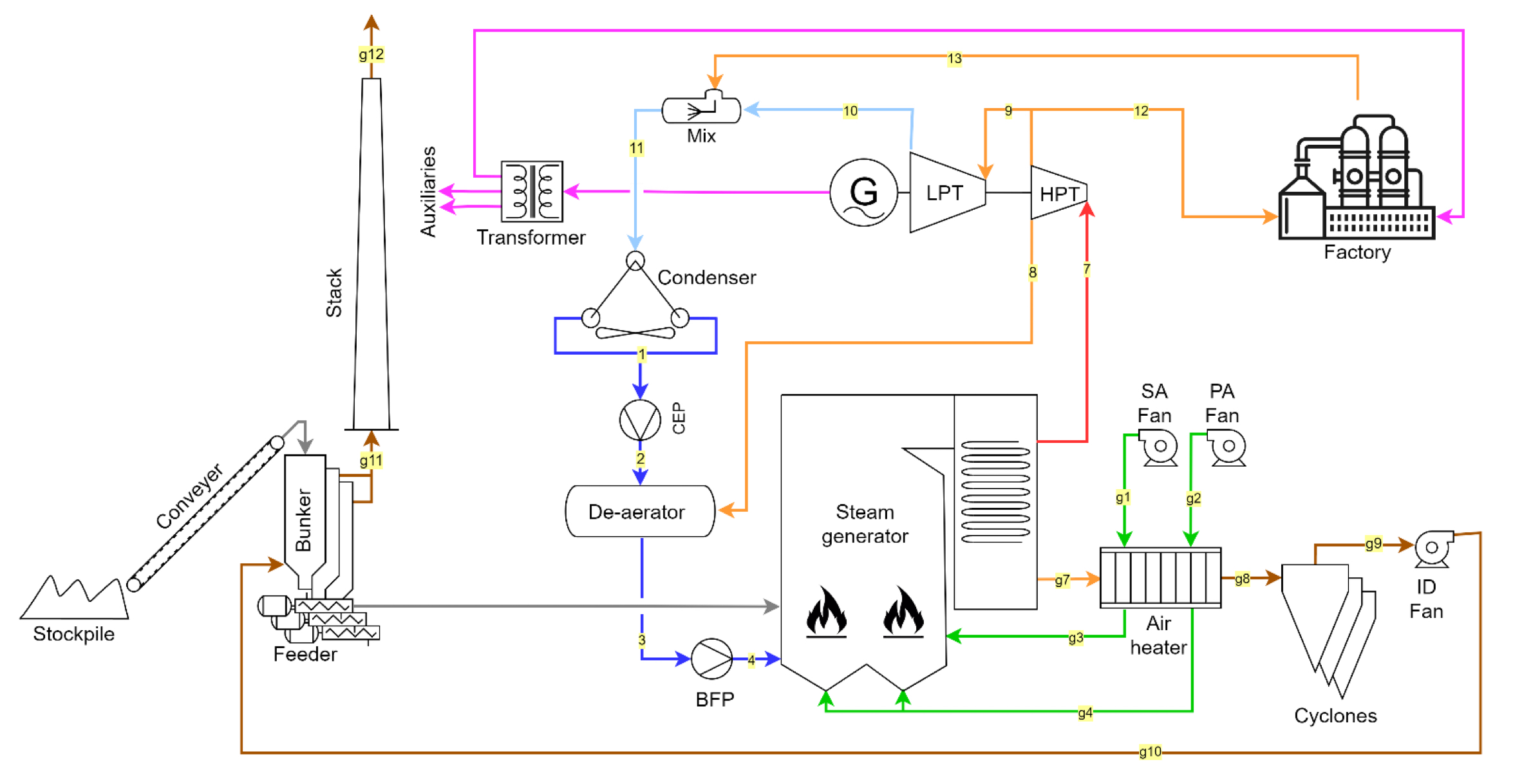

Simplified Power Plant Specification

2023

A systems engineering project involving the design of a simplified Biomass Steam Power Plant generator.

Responsible for the Steam Generator's basic design, utilizing high-level cycle analysis to optimize for efficiency and cost effectiveness within defined user requirement specifications.

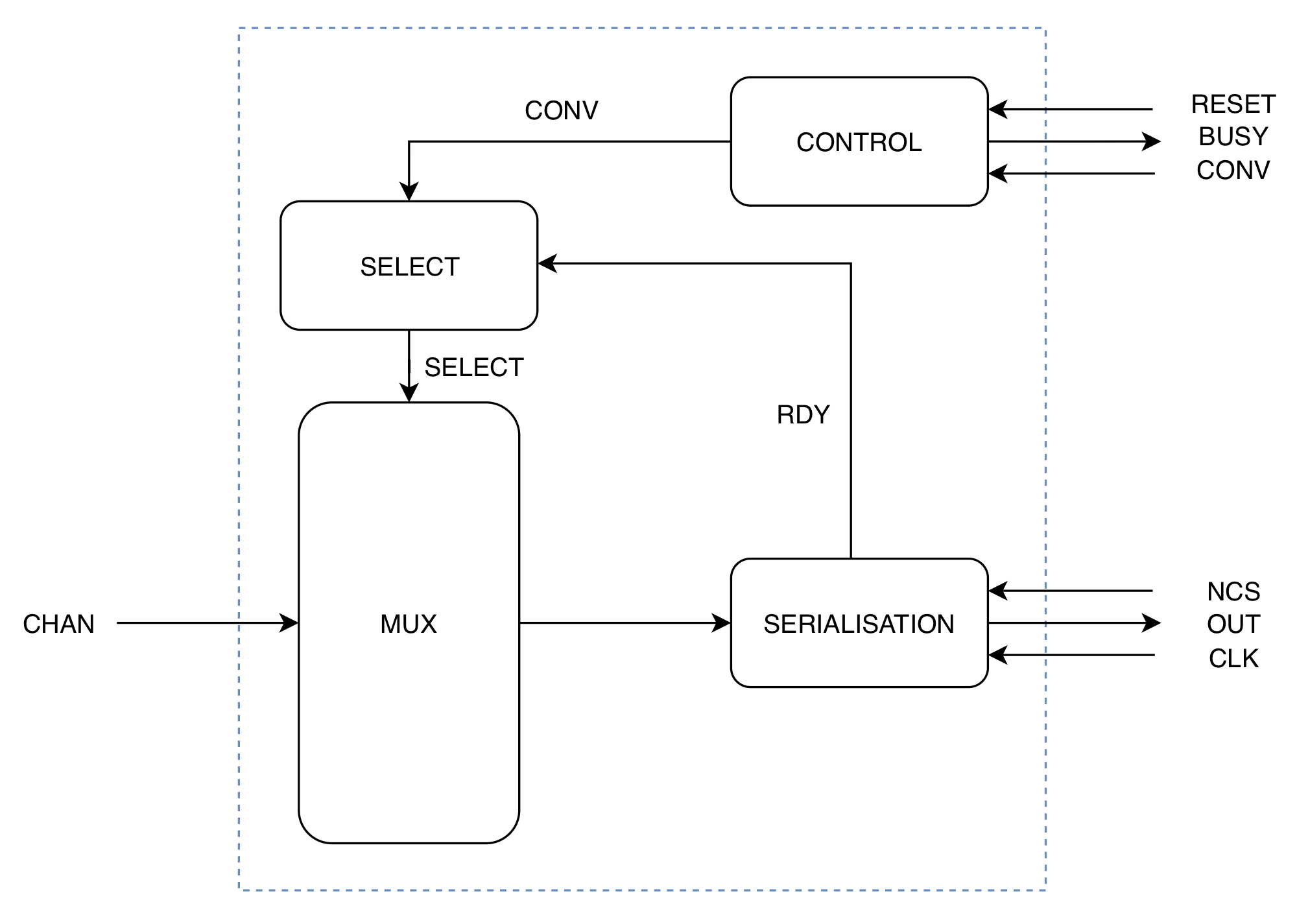

VHDL model of an ADC

2022

A synthesisable VHDL Model of an Analog to Digital Converter (ADC) for firmware and interface testing.

Developed as a verification tool to enable on-target firmware testing. The model accurately reflects the I/O and timing specifications defined in the hardware datasheet.

Want to find out more about any of the projects?

Contact Me.